Invasive Tightly-Coupled Processor Arrays (B02) (SFB/TRR 89 InvasIC (B02))

Third Party Funds Group - Sub project

Acronym: SFB/TRR 89 InvasIC (B02)

Start date : 01.07.2010

End date : 31.12.2022

Website: http://invasic.informatik.uni-erlangen.de/en/tp_b2_PhIII.php

Overall project details

Overall project

DFG SFB/Transregio 89 "Invasive Computing" (TRR 89)

July 1, 2010 - Dec. 31, 2022

Project details

Short description

Short description

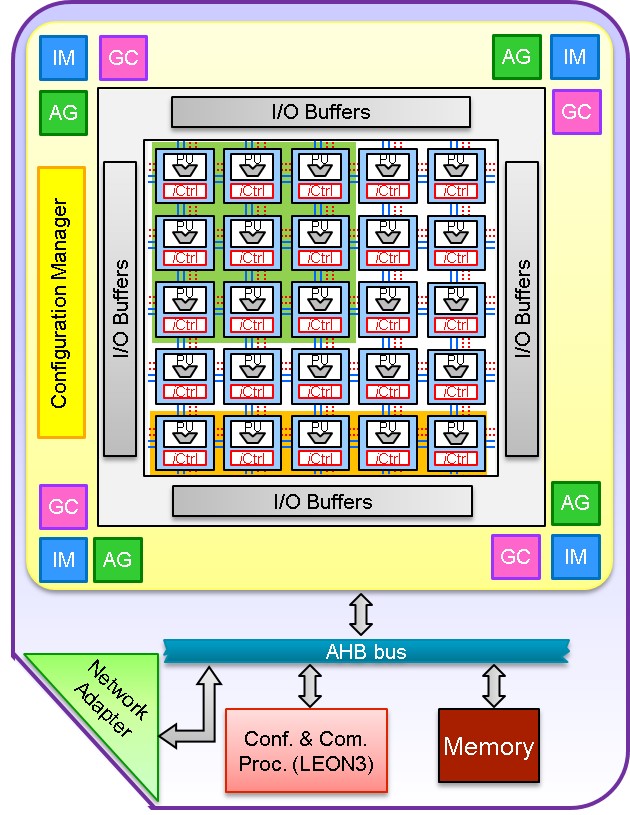

Micro- and macroarchitectural research to support the hardware-controlled cycle-wise invasion of tightly-coupled processor arrays (TCPAs). The investigations include techniques for enabling (a) fault tolerance (DMR, TMR) through invasion of redundant array regions of processors as well as novel hardware concepts for reaction and recovery from faults, (b) orthogonal instruction processing as a new concept for increasing the code density of the VLIW cores of a TCPA, and (c) methods for fine-granular power management of TCPA regions in trade-off between predictable yet energy-efficient computing as well as in view of dark silicon.

Scientific Abstract

TCPAs provide a platform for the highly time-predictable and ultra-low power implementation of parallel loop nests. Yet, as loop bounds may often be unknown at compile-time, new techniques for (a) self-invasion are required to determine claim sizes and perform (b) self-power adjustment and (c) self-selection of redundancy schemes at run time to enforce throughput, latency, power and reliability requirements. Moreover, to lift TCPAs to new application areas, (d) novel floating point processors with invadable precision (FloaTCPAs) including (e) functional units with programmable latency to compute instructions approximately will be investigated.